VOICE OF THE ENGINEER

Issue 2/2007 www.edn.com

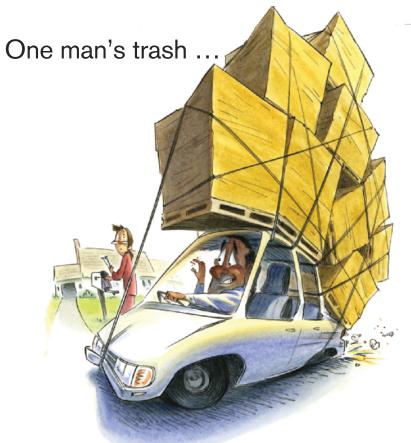

One man's trash ... Pg 36

**EDA Consortium:** the Market Statistics Service Pg 10

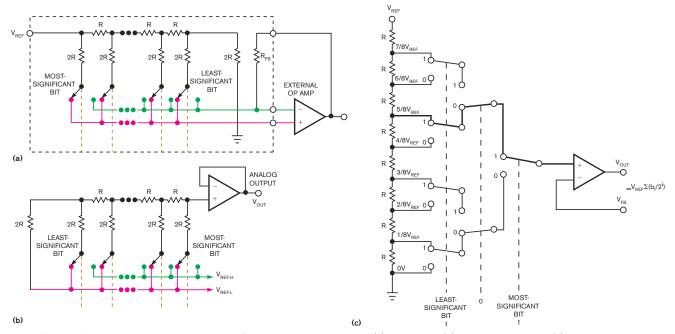

**Bonnie Baker** compares DAC architectures Pg 34

Seeking the secrets of a satellite receiver Pg 38

Design Ideas Pg 83

SHORT CUTS Page 58

# **BEYOND SPICE**

Page 41

Agile software empowers wirelesssensor networks Page 67

A logical approach to NVM integration in SOC design

Page 73

Now the LeCroy toolbox is more powerful than ever in oscilloscopes you didn't know you could afford. From 200 MHz to 2 GHz, LeCroy scopes offer more analysis and debug tools than anyone else at prices from \$3,000. So what are you waiting for? Find the right tool for your design debug job at LeCroy. We're all about the tools.

# RECEIVE A FREE PRODUCT CATALOG!

Now Featuring: More Wireless Components Than Ever!

Visit www.digikey.com/catalog

Quality Electronic Components, Superior Service

www.digikey.com • 1.800.344.4539

701 Brooks Ave. South • Thief River Falls, MN 56701 • USA

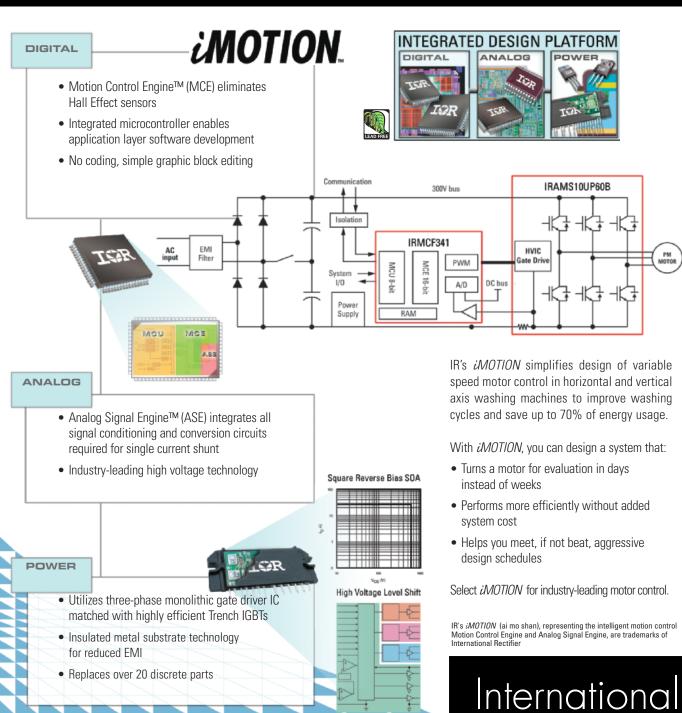

# SIMPLE, SENSORLESS CONTROL FOR DIRECT DRIVE WASHERS

Simplify Design, Improve Efficiency, Accelerate Time-to-Market

for more information call 1.800.981.8699 or visit us at www.irf.com/motion

Rectifier

THE POWER MANAGEMENT LEADER

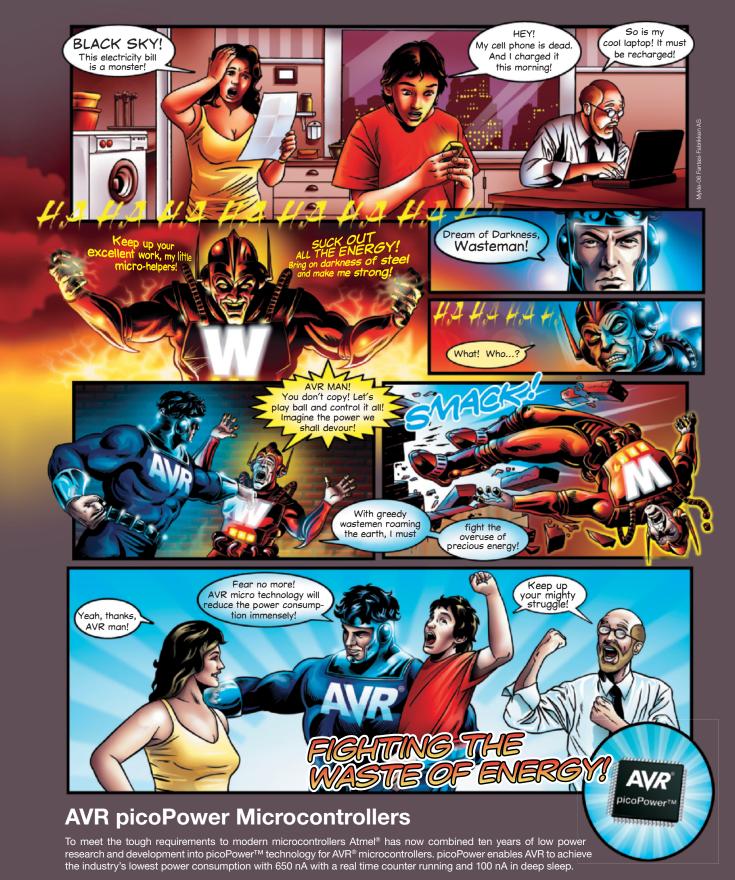

What can AVR picoPower do for your design?

- What can AVR picoPower True 1.8V supply voltage enabling operation of all features and core down to 1.8V

- Minimized leakage current enabling 100 nA Power Down sleep consumption

- Sleeping brown-out detector enabling full protection with no power penalty

- Ultra low power 32 kHz crystal oscillator enabling operation at only 650 nA

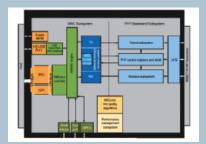

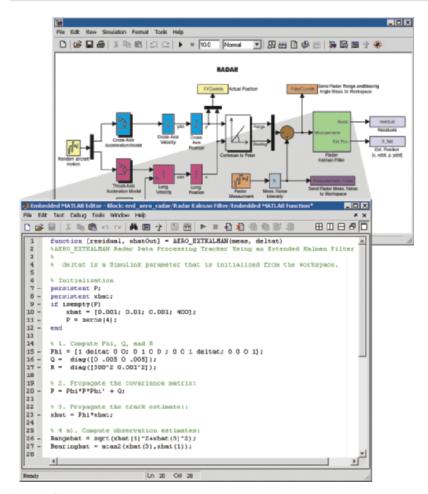

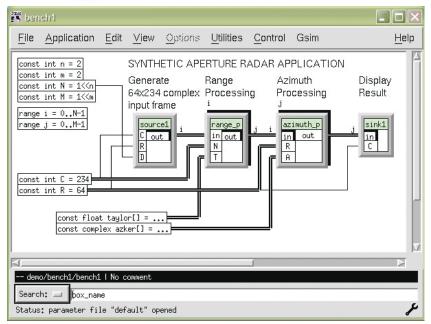

# **Design 10X Faster**

with Graphical System Design

# **Graphical System Design**

Accelerate your embedded design using National Instruments LabVIEW graphical programming, third-party tools, and commercial off-the-shelf hardware. Graphical system design empowers you to rapidly design, prototype, and deploy embedded systems.

# **DESIGN**

- > Control design

- > Intellectual property libraries

- > Digital filter design

- > Dynamic system simulation

# **PROTOTYPE**

- > I/O modules and drivers

- > COTS FPGA hardware

- > VHDL and C code integration

- > Design validation tools

# **DEPLOY**

- > Rugged deployment platforms

- > Distributed networking

- > Human-machine interfaces

- > Firmware management

"With graphical system design through NI LabVIEW and CompactRIO, we designed a motorcycle ECU prototyping system in three months versus two-and-a-half years with traditional tools."

Carroll Dase, design engineer Drivven, Inc.

Learn how to design faster through Webcasts by Analog Devices, Celoxica, and Maplesoft at **ni.com/design**.

(800) 450 8999

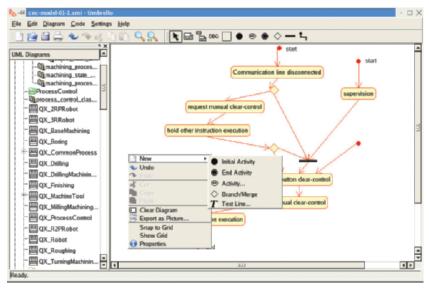

# Model behavior: creating embeddedsoftware short cuts

As embedded-system teams race to bring new products to market, designers are evaluating model-based development tools to deal with escalating software complexity.

by Warren Webb, Technical Editor

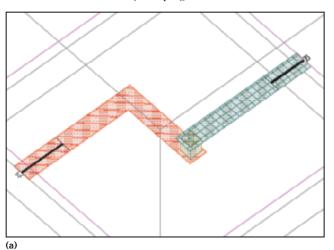

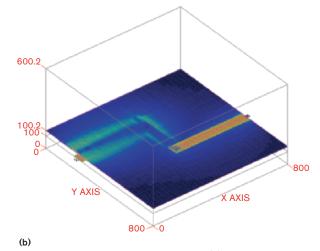

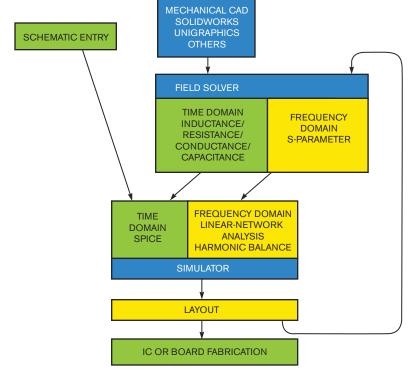

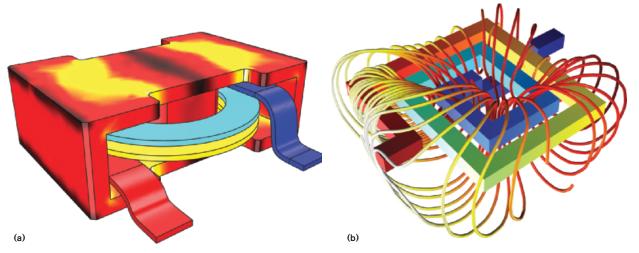

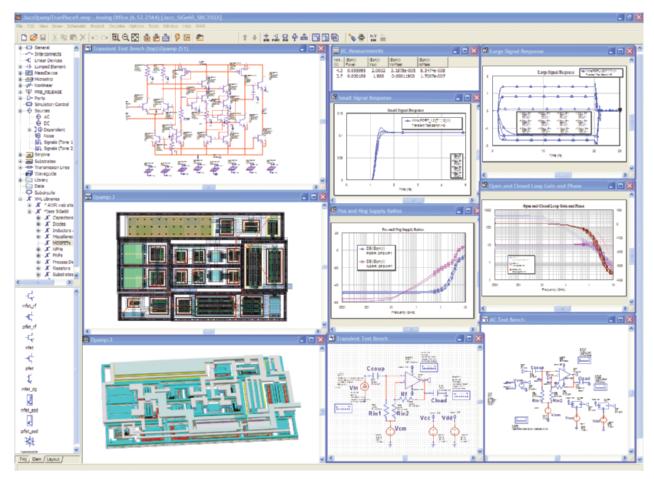

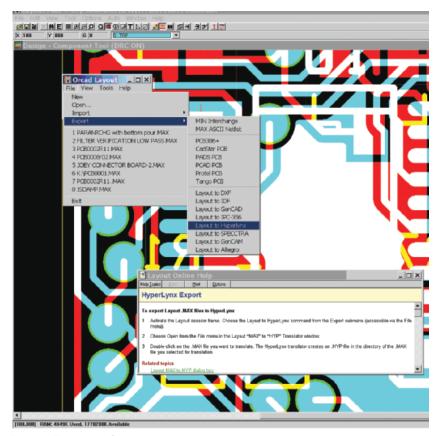

# **Beyond Spice**

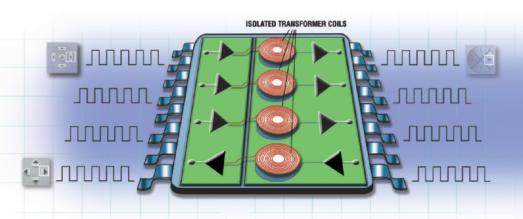

Field-solver software can predict the behavior of circuits that operate at speeds and densities beyond the capabilities of Spice to properly model. Whether you are trying to verify signal integrity or designing an RFIC, you should know how field solvers could help your

by Paul Rako, Technical Editor

# EDN contents

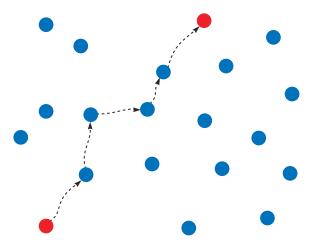

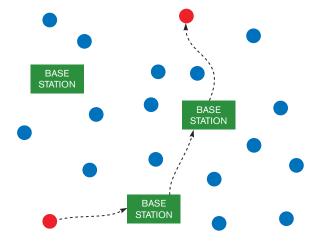

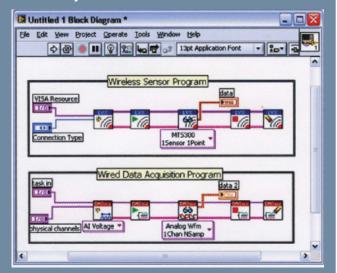

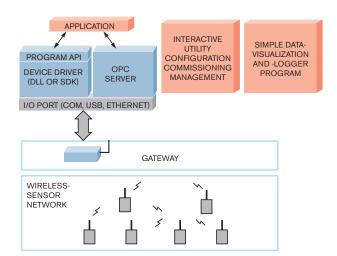

# Agile software empowers wirelesssensor networks

Applications for wireless networks can range from home automation to large-scale environmental monitoring. With the freedom these wireless approaches offer, you can network the tundra as easily as the office.

> by PJ Tanzillo, National Instruments

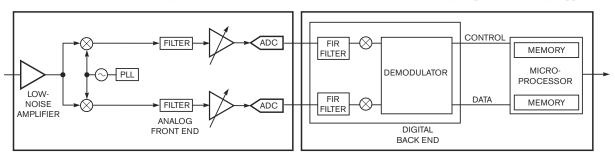

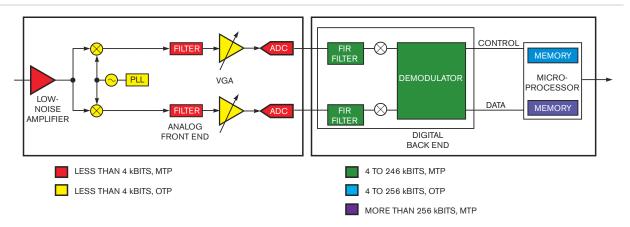

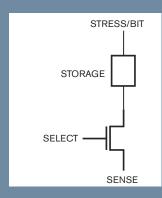

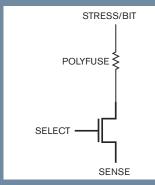

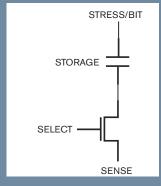

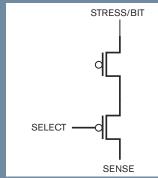

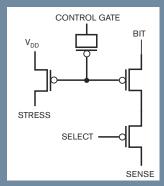

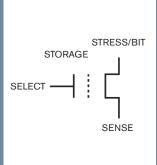

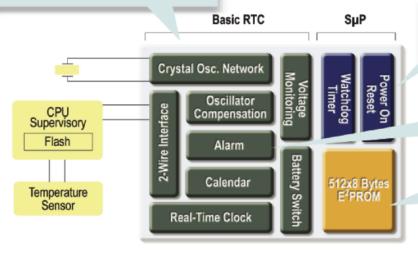

# A logical approach to NVM integration in SOC design

SOC designers have several options for integrating NVM (nonvolatile memory) into their designs, so it's wise to weigh the availability and numerous trade-offs before jumping headfirst into integrating NVM into your SOC.

> by Ann De Vries and Yanjun Ma, Impinj

# SIGNIDEAS

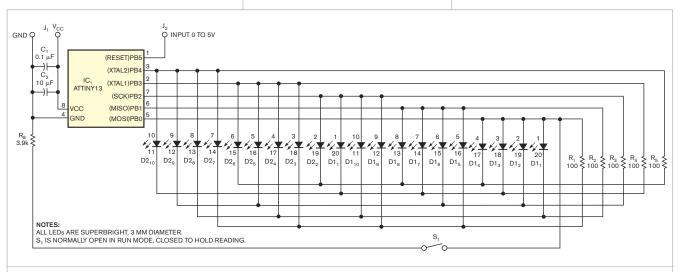

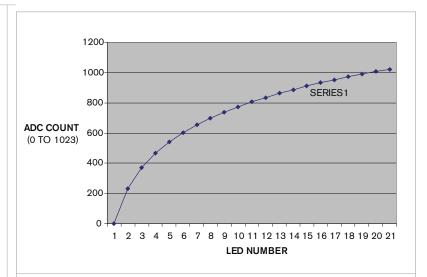

- 83 Microcontroller drives logarithmic/linear dot/bar 20-LED display

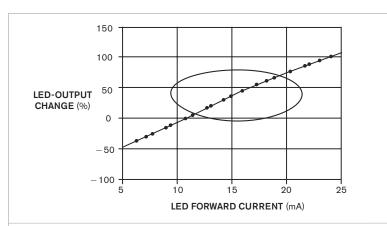

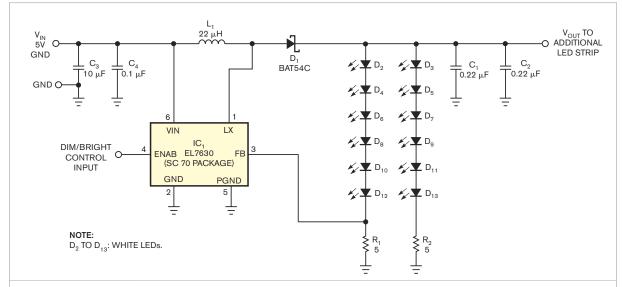

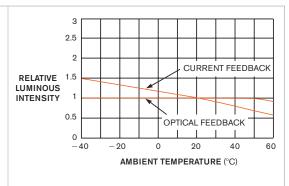

- 84 Optical feedback extends white LEDs' operating life

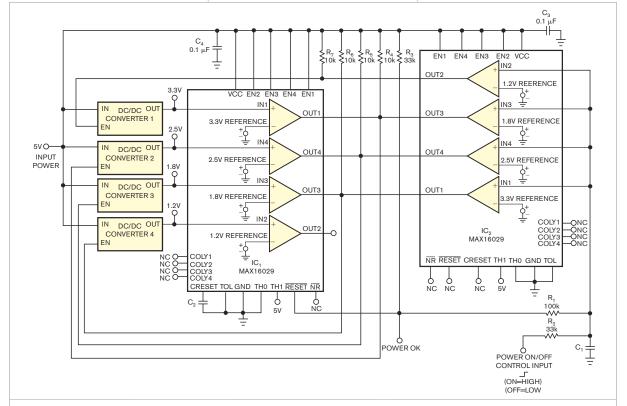

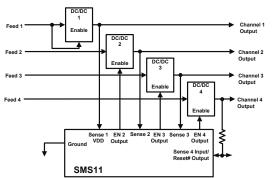

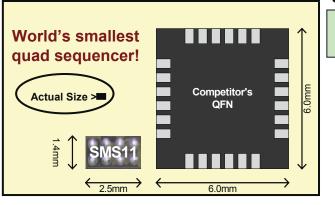

- 88 Sequencer controls power supplies' turn-on and turn-off order

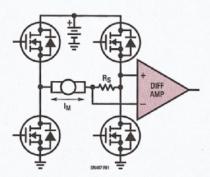

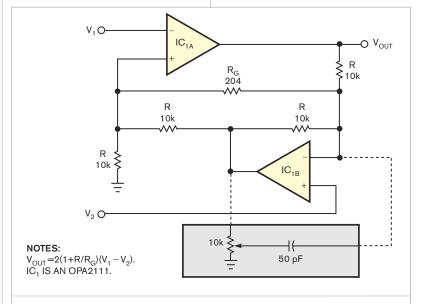

- 92 Use dual op amp in an instrumentation amp

# Design with confidence.

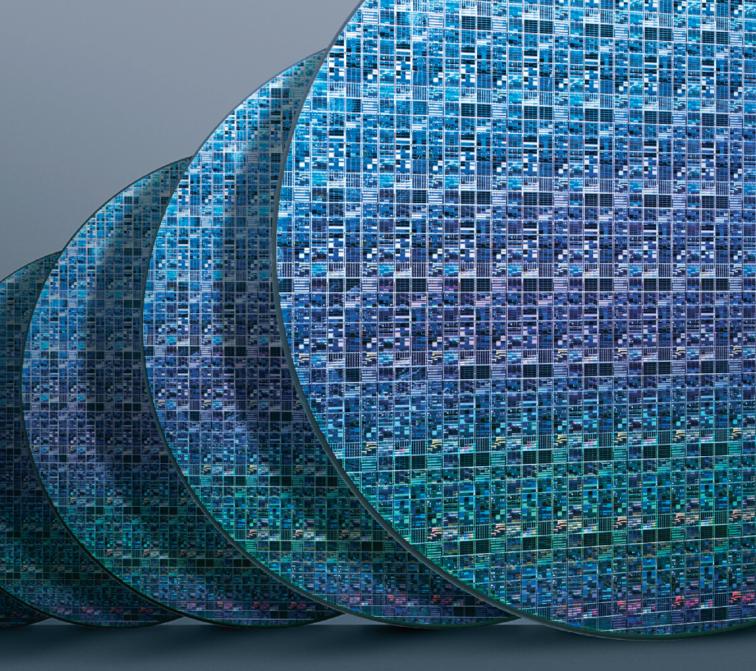

Introducing the new Stratix III family.

# Stratix III Family: The Lowest-Power High-Performance FPGAs

Building on the success of prior generations, Stratix® III FPGAs give you the highest performance available, while keeping power consumption to a minimum.

Design your next-generation systems with confidence.

Design with Stratix III FPGAs.

Supported by

The Programmable Solutions Company®

www.altera.com/confidence

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights.

# contents 1.18.07

- 25 Software tests compliance with eight popular protocols

- 26 Low-cost, high-I/O-count FPGAs target display market

- 26 Data-acquisition module features USB interface

- 28 IEEE 802.11n wireless-LAN market remains in conflict as draft-n battle looms

- 28 Practical book helps developers apply USBinterfaced mass-storage devices

- 30 Model-based DFM platform emerges

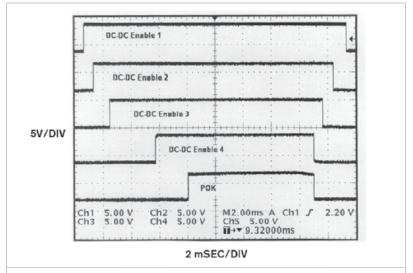

- **Voices:** Cherokee International: Where in the world are design and manufacturing?

# DEPARTMENTS & COLUMNS

- 10 EDN.comment: EDA Consortium: the Market Statistics Service

- 34 **Bonnie Baker:** Comparing DAC architectures

- 36 Tales from the Cube: One man's trash ...

- **Prying Eyes:** Seeking the secrets of a satellite receiver

- 106 Scope: APEC 2007, document-quality printing, and developing-country electronics

# PRODUCT ROUNDUP

- 97 Optoelectronics/Displays: LED bulbs, charge pumps, fiber-optic LED transmitters, digital optocouplers for hybrid vehicles, and more

- 98 Computers and Peripherals: High-performance monitors, DVD-RAM drives, graphics cards, and more

- 100 Test and Measurement: In-circuit and debugging emulators

- 103 Integrated Circuits: Audio/video decoders, floating-point DSPs, and more

EDN® (ISSN#0012-7515), (GST#123397457, R.B.I. Intl Pub Mail #0280844) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer; Stephen Moylan, President, Boston Division. Periodicals postage paid at Littleton, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2007 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$165 one year; Canada, \$226 one year, (Includes 7% GST, GST#123397457); Mexico, \$215 one year; air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Mail Agreement No. 40685520. Return undeliverable Canadian addresses to: Deutsche Post, 4960-2 Walker Road, Windsor ON N9A 6J3. E-mails: subsmail@reedbusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc. used under licenses. A Reed Business Information Publication/Volume 52, Number 2 (Printed in USA).

### XBee™ ZigBee OEM RF Module

ZigBee/IEEE 802.15.4 compliant solution that delivers critical data between devices. Operates within the ISM 2.4GHz-frequency band, 1mW power output up to 100m range, U.FL.RF connector, -40°C to 85°C temp. range, and chip or wire options. Supports advanced networking and low-power modes.

XPort™ AR contains all the essential device computing and networking features built into a single RJ45 package, including a 120Mhz DSTni™ processor, 10/100 Base-T/TX Ethernet connection, an embedded web server, and a full network operating system with TCP/IP protocol stack.

# **Embedded Products for** the Latest Technologies

Rabbit Semiconductor BL2600 Wolf™

Reduced time to market is critical for new product designs -- lost time means lost revenue. That's why engineers depend on Mouser to deliver a broad selection of embedded products

And because these components have a solution designed in, engineers can utilize these plug-and-play modules from test through production - saving time and money.

Experience Mouser's time-to-market advantage! Our vast selection of the NEWEST products, NEWEST technologies, new catalog every 90 days, no minimums, and same-day shipping on most orders, gets you to market faster. We make it easy to do business with

mouser.com

(800) 346-6873

The Newest Products For Your Newest Designs

# FlashDisk Module

Provides non-volatile, solid state data and program storage for embedded applications. Operating system, application software compatibility,

and portability is ensured by the module's True IDE interface. No moving parts allow for more rugged and reliable performance than rotation hard drives.

# SimpleTech. mouser.com/simpletech/a

# **High-Performan** Microprocessor

Low EMI microprocessor for embedded control, communications, and Ethernet connectivity. Glueless architecture, 10Base-T Ethernet, C-friendly instruction set. Up to 60MHz, 8 independent DMA channels, supports 8 or 16-bit Flash and SRAM memories, 7 hardware breakpoints, 40+ I/O lines.

mouser.com/rabbitsemi/a

# MOD5282 32-bit **Processor** Module

32-bit 66MHz ColdFire

processor with 10/100 Ethernet, 3 UARTs, 8 10-bit ADC, I2C, SPI, and 50 digital I/O. Comprehensive software package consists of uC/OS RTOS, TCP/IP stack, web server, NetBurner Eclipse IDE with C/C++ compiler, and debugger.

mouser.com/netburner/a

# ED online contents

# ONLINE ONLY

Check out these Web-exclusive articles:

### WiQuest adds video support to Wireless USB

For months now, rarely a week has passed when one Wireless USB player or another hasn't touted a chip compatible with the specifications that the WiMedia Alliance has shepherded.

www.edn.com/article/CA6401216

# Denali offers MLC and SLC NANDcontroller core, development software

Denali Software Inc is expanding its implementation IP (intellectual-property) portfolio, introducing a new controller core for MLC (multilevel-cell) and SLC (singlelevel-cell) NAND devices.

www.edn.com/article/CA6401727

### Blaze DFM's dummy-fill-synthesis tool has smarts

Blaze DFM is following up its mid-2006 release of its Blaze MO gate-CD biasing/leakage control tool with a dummy-fill "synthesis" tool.

www.edn.com/article/CA6400204

# INTRODUCING: BEDDED PROCESSING

In this new blog, Technical Editor Robert Cravotta explores processor and softwareprocessing architectures and the impact they have on system and software development.

www.edn.com/processing

# READERS' CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

### Cutting the carbon-energy cord: Is the answer blowin' in the wind?

www.edn.com/article/CA6399098

# Harvesters gather energy from the ether, power lightweight systems

www.edn.com/article/CA6399099

#### The Hot 100 products of 2006

www.edn.com/article/CA6399100

#### Three microcontroller ports drive 12 LEDs

www.edn.com/article/CA6399101

# Magnetic-field probe requires few components

www.edn.com/article/CA6399102

### Dynamic siphon steals current from USB port

www.edn.com/article/CA6399103

# Broadband connections: A day isn't always a day, but a byte is a byte

www.edn.com/article/CA6399104

### Hard-disk-drive seminar discusses road map for PMR

www.edn.com/article/CA6399873

# Simple tester checks Christmas-tree

www.edn.com/article/CA46423

# Simple scheme saves string-light

www.edn.com/article/CA46448

# **INNOVATION AWARDS**

#### **TICKETS ON SALE NOW!**

Tickets for EDN's annual Innovation Awards banquet are now on sale. The event will take place April 2, 2007, in San Jose, CA. Visit www.edn.com/innovation for more details and to order your tickets today. Order before February 2 and receive the special early-bird ticket price.

# HOT 100 PRODUCTS of 2006

As 2007 gets underway and we prepare for a whole new batch of hot products in the year to come, take a look back at the ones to beat from 2006! Our list distills the most innovative and significant products of the year, including process technologies, power sources, storage devices, processors, intellectual-property cores, communication controllers, test instruments, embedded boards, EDA tools, and more.

www.edn.com/2006hot100

# BY ROBERT GARDNER, EXECUTIVE DIRECTOR, EDAC

# EDA Consortium: the Market Statistics Service

ditor's note: In two 2006 columns, *EDN* Senior Editor Mike Santarini took EDAC (Electronic Design Automation Consortium) to task for changes in how they report market numbers (www.edn.com/article/CA6387027 and www.edn.com/article/CA6298273. EDAC's Executive Director Robert Gardner responds here to those columns.

I'd like to shine some light on EDAC's MSS (Market Statistics Service) and talk about the value it provides. EDAC created the MSS more than 10 years ago to give industry members timely information about EDA revenue by market segment. The MSS releases the top-line industry-revenue numbers to the public each quarter, and paying subscribers receive breakdowns by more detailed product segments. The service is available for purchase from EDAC, with discounts for consortium members and companies that report their own data.

Although some have compared the MSS report with the Gartner/Data-quest report, it actually serves a different purpose. The Gartner/Data-quest report was perhaps the best-known and most detailed source of market numbers in EDA, providing market-share numbers and segment-growth forecasts. Gartner/Dataquest, however, published only annual numbers. The EDAC MSS report focuses on providing a quarterly snapshot of EDA revenue by product categories and region, offering a timely barometer of the industry.

The MSS has reported SIP (semiconductor-intellectual-property) data as a separate category since 1997, so

it isn't a new addition. From 1997 to 2004, the MSS SIP category grew from having two subcategories to six subcategories. In addition, EDAC's quarterly press announcements publicly broke out SIP market-segment revenue. As IP (design reuse) became an increasing part of both EDA customers' speeding their designs to market and the product lines of many EDA companies, it made sense for EDAC to review the SIP-category reporting. In 2004, EDAC announced its work with the VSIA (Virtual Socket Initiative Alliance) to define approximately 40 additional SIP-product subcategories for the MSS. When making this decision, EDAC consulted with the VSIA to determine reasonable SIP-product subcategories. We also continued to reach out to IP companies to report their revenue numbers to EDAC. IP companies have since joined EDAC, and two of their leaders have joined our board: John Bourgoin, president and chief executive officer of MIPS Technology, and Sanjay Srivastava, president and chief executive officer of Denali Software. Another change that took place is that, in October 2005, EDAC announced its decision to include the publicly available numbers of nonreporting IP companies. EDAC includes all available market data to give the best picture of what's happening in the SIP-product segments. EDAC separately breaks out the nonreporting IP companies in the report so that a recipient of the report can exclude them from analysis if he or she wishes.

The inclusion of IP data does, of course, change the overall revenue that the MSS reports, but recipients of the report still get the full breakdown by product segment. The process is transparent, and any company that doesn't wish to include IP in its own internal analysis of the market can remove it.

To ensure the integrity of reporting, individual companies report their revenue—divided into the established product segments—to audit company PriceWaterhouseCoopers. The audit company then reports total revenue by product segment, as well as by region.

Like any other report about a dynamic market, this report's results are approximate. New companies or segment reporting can create year-over-year comparison issues in the data. EDAC handles these issues by providing complete listings of all companies included in each segment's numbers. Each user of the report has complete information, so they can judge how best to use the data.

The MSS is a great service that provides useful data at an affordable price. The quarterly release of revenue breakdown by major category (computer-aided engineering, pc boards and multichip modules, IC physical design and verification, and SIP) is only a small piece of the entire report. If you have interest in EDA-market data, EDAC encourages you to examine the full report.EDN

# MORE AT EDN.COM

+ Go to www.edn.com/070118ed and click on Feedback Loop to post a comment on this column.

# These new ultrathin inductors really shine in LED and EL backlight applications

Our new LPS shielded inductors give you the best combination of ultralow profile and high level performance.

**Highest saturation current ratings** Compared to competitive inductors of the same size, our Isat ratings are typically 20 - 30% higher.

Widest range of L values Only Coilcraft's LPS family offers you so many inductance options: from 3300 µH all the way down to 0.33 µH.

And no one else has so many high inductance values in a 3x3 mm footprint.

**Rugged construction** Their impact-resistant design withstands 1500 G's deceleration in one meter drop tests, making them the perfect inductors for handheld devices.

See why designing in our new LPS inductors is a really bright idea. Visit www.coilcraft.com/lps3

# **The Ultimate in Ethernet PHY Solutions**

10BASE-T/100BASE-TX Physical Layer Transceiver with MII/RMII Interfaces Media Player **Entertainment System** DSL Set-top Box 45 KSZ8041NL Print Server & Printer Game Console

Micrel's KSZ8041NL provides the ultimate in Ethernet PHY solutions. The KSZ8041NL has the industry's smallest package, 5mm x 5mm MLF™, industry's lowest power consumption of less than 180mW and the highest ESD ratings for a Fast Ethernet transceiver at 6KV. The KSZ8041NL is ideal for applications where board real estate is at a premium, where low power is important, and where stringent ESD conditions apply, such as in Industrial Ethernet environments. In addition, at 6KV ESD, the chip exceeds the ESD requirements for most industrial applications.

For more information, contact your local Micrel sales representative or visit us at: www.micrel.com/ad/ksz8041nl.

Literature: 1 (408) 435-2452 Factory: 1 (408) 944-0800

www.micrel.com

# Good Stuff:

- ◆ Single chip 100BASE-TX/10BASE-T physical layer solution

- ◆ Low power CMOS design, power consumption of ~180 mW

- ◆ Robust operation over standard cables

- Supports Media Independent Interface (MII), Reduced MII (RMII)

- ◆ Supports HP MDI/MDI-X auto crossover

- ◆ Supports power down mode and power saving mode

- ◆ MDC/MDIO for rapid configuration

- ◆ Fully compliant to IEEE 802.3u standard

- Supports auto-negotiation and manual selection for 10/100Mbps speed and full/half-duplex mode

- ◆ Single Power Supply (3.3V)

- ◆ 32-pin MLF<sup>™</sup> (QFN per JEDEC) package

© 2007 Micrel, Inc. All rights reserved. Micrel is a registered trademark of Micrel, Inc. MLF is a registered trademark of Amkor Technology.

# **EDN**

#### PUBLISHER. EDN WORLDWIDE

John Schirmer 1-408-345-4402: fax: 1-408-345-4400: jschirmer@reedbusiness.com

#### EDITOR IN CHIEF

Maury Wright, 1-858-748-6785; mgwright@edn.com

#### **EXECUTIVE EDITOR**

Ron Wilson, 1-408-345-4427; ronald.wilson@reedbusiness.com

#### MANAGING EDITOR

Kasev Clark

1-781-734-8436; fax: 1-781-290-3436; kase@reedbusiness.com

### **EXECUTIVE EDITOR. ONLINE**

Matthew Miller

1-781-734-8446: fax: 1-781-290-3446: mdmiller@reedbusiness.com

### SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-781-290-3307; moleary@reedbusiness.com

#### EMBEDDED SYSTEMS

Warren Webb, Technical Editor 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com

#### ANALOG

Paul Rako, Technical Editor 1-408-745-1994: paul.rako@reedbusiness.com

#### EDA, MEMORY, PROGRAMMABLE LOGIC

Michael Santarini, Senior Editor 1-408-345-4424;

michael.santarini@reedbusiness.com

#### MICROPROCESSORS, DSPs, TOOLS

Robert Crayotta, Technical Editor 1-661-296-5096: fax: 1-781-734-8070: rcravotta@edn.com

#### MASS STORAGE, MULTIMEDIA. **PCs AND PERIPHERALS**

Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-781-734-8038; bdipert@edn.com

### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

#### DESIGN IDEAS EDITOR

**Brad Thompson** edndesignideas@reedbusiness.com

### SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439; fax: 1-781-290-3439: f.granville@reedbusiness.com

#### ASSOCIATE EDITOR

Maura Hadro Butler, 1-908-347-9605; mbutler@reedbusiness.com

#### EDITORIAL/WEB PRODUCTION MANAGER

Diane Malone, Manager 1-781-734-8445; fax: 1-781-290-3445 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442; fax: 1-781-290-3442 Melissa Annand, Newsletter/Editorial Coordinator Contact for contributed technical articles 1-781-734-8443; fax: 1-781-290-3443 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-781-290-3325

### CONTRIBUTING TECHNICAL EDITOR

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Jones, Production Manager 1-781-734-8328; fax: 1-781-734-8086 Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-781-734-8086

#### **EDN EUROPE**

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; aprophet@reedbusiness.com

#### EDN ASIA

Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirtimaya Varma, Editor in Chief kirti.varma@rbi-asia.com

#### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Kenji Tsuda, Editorial Director and Editor in Chief tsuda@reedbusiness.ip Takatsuna Mamoto, Deputy Editor in Chief t.mamoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

#### **DENNIS BROPHY**

Director of Business Development, Mentor Graphics

# DANIS CARTER

Principal Engineer, Tyco Healthcare

#### CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne

#### DMITRII LOUKIANOV

System Architect Intel

#### RON MANCINI Engineer

**GABRIEL PATULEA** Design Engineer, Cisco

#### MIHIR RAVEL

VP Technology, National Instruments

#### DAVE ROBERTSON

Product Line Director, Analog Devices

#### SCOTT SMYERS

VP Network and System Architecture Division, Sony

TOM SZOLYGA Program Manager, Hewlett-Packard

#### JIM WILLIAMS

Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000; fax 1-781-734-8070. Address changes or subscription inquiries: phone 1-800-446-6551; fax 1-303-470-4280; subsmail@reed business.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

# **Logic Analysis** to Digital ATE

# **High-Speed Digital I/O**

As part of the National Instruments mixed-signal suite, high-speed digital modules from NI offer the flexibility and features to address applications ranging from digital interfacing to advanced digital test.

| Features                 | Programmable<br>DIO          | LVDS<br>DIO | PCI Express<br>DIO    |

|--------------------------|------------------------------|-------------|-----------------------|

| Bus                      | PXI, PCI                     | PXI, PCI    | PCI Express           |

| Data Rate                | 100 Mb/s                     | 400 Mb/s    | 50 Mb/s               |

| Channels                 | 20                           | 16          | 32                    |

| Voltage                  | -2 to 5.5 V<br>(10 mV steps) | LVDS        | 2.5, 3.3,<br>or 5.0 V |

| Triggering               | /                            | /           | /                     |

| Scripting                | /                            | /           | _                     |

| Hardware                 | ✓                            | _           | -                     |

| Compare                  |                              |             |                       |

| Applicatio               | ns                           |             |                       |

| Logic<br>Analysis        | 1                            | ✓           | ✓                     |

| Pattern<br>Generation    | 1                            | ✓           | ✓                     |

| BERT                     | /                            | -           | -                     |

| Digital ATE              | ✓                            | -           | -                     |

| Sustainable<br>Streaming | -                            | -           | 1                     |

To compare specifications and view application videos for the NI high-speed digital modules, visit ni.com/highspeeddigital.

(800) 891 8841

© 2006 National Instruments Corporation. All rights reserved. National Instruments, NI, and ni.com are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective companies. 2006-6933-501-101-D

# DESIGN GON 2007

Connecting the World of Electronic Design

# FREE Exhibition Pass

A \$75 Value

*January 29 – February 1, 2007*

Santa Clara Convention Center Santa Clara, California

Bring this pass to the Santa Clara

Convention Center to gain FREE

access to the following and be

entered to win one of many

fabulous high-tech prizes!

125+ Exhibitors

Plenary and Technical Panels

Technology Pavilions

- Keynote Addresses

- TecPreviews

- Networking Receptions

International Engineering Consortium www.iec.org

www.designcon.com/2007

# Why settle for a slice?

# When you can have the whole pie...

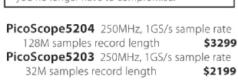

# PicoScope 5000 Series USB 2.0, PC Oscilloscopes

pico

PicoScope<sup>®</sup>

PicoScope 6 capture and analysis software

# The No Compromise PC Oscilloscopes

With class-leading bandwidth, sampling rate, memory depth and an array of advanced high end features the PicoScope 5000 PC Oscilloscopes give you the

features and performance you need without any compromise.

### Advanced triggers

In addition to the standard triggers the PicoScope 5000 series comes standard with pulse width, window, dropout, delay, and logic level triggering.

- 250MHz Spectrum analyzer

- High speed USB 2.0 connection

- Automatic measurements

- Arbitrary waveform generator

Define your own waveforms or select from 8 predefined signals with the 12 bit, 125MS/s arbitrary waveform generator

# 250 MHz Bandwidth

# 128M Sample Record length

All other oscilloscopes at this price range force you to compromise on one of three key specifications: bandwidth, sampling rate or record length. With the PicoScope 5000 series you no longer have to compromise.

for information call 1.800.591.2796

# At Last!

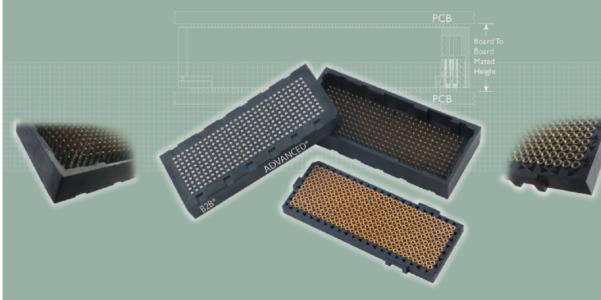

# A Surface Mount Connector That Won't Crack Under Pressure

TELECOM | COMPUTERS | PERIPHERALS | MEDICAL | DATA STORAGE | MILITARY

IC SOCKETS AND ADAPTERS

Products shown may be covered by patents issued and/or pending

Our new line of B2B® SMT Connectors can stand up to the most rigorous board stacking applications.

- Screw-machined terminals with multi-finger contacts for mission critical reliability (rated up to 500 cycles)

- Robust molded LCP insulators with integral keying features ensure positive polarization and allow for blind mating

- Standard eutectic or RoHS compliant lead-free solder ball terminals for superior processing results

- Available in industry-standard 1.27mm pitch footprints for mated heights of 6.0mm, 8.0mm, and 12.7mm

- Custom designs available

To learn more, visit us online at http://www.advanced.com or call 1.800.424.9850.

**ISO** 9001

# SIGNAL PATH designer®

Tips, tricks, and techniques from the analog signal-path experts

No. 108

Feature Article....1-7

Pressure Force Load Testing......2

Factory Automation

Solutions.....4-5

Design Tools.....8

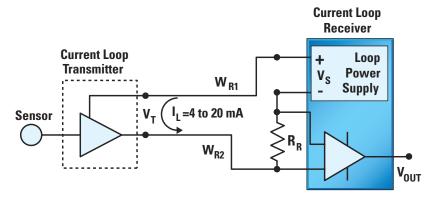

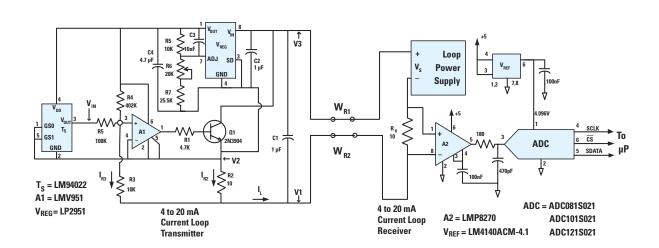

# **Low-Voltage Current Loop Transmitter**

— By Walt Bacharowski, Applications Manager

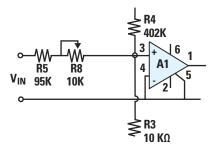

**Figure 1. Current Loop Components and Connection**

he 4 to 20 mA current loop, which is used extensively in industrial and process control systems, creates challenges for maximizing the operating loop length. In some cases, a very long loop is required and the combination of limited loop-power supply voltage and excessive loop wire resistance prevents it use. This article discusses the use of low-voltage amplifiers to minimize the transmitter's operating voltage requirements, which will maximize the operating loop length.

Typically, the current loop is powered from the receiver side while the transmitter controls the current flowing in the loop to indicate the value of the physical parameter being measured by the sensor. *Figure 1* shows the basic components and connection of a current loop.

The maximum distance between the transmitter and receiver is dependent on the power supply voltage  $(V_S)$ , and the sum of the loop drops, which are the minimum transmitter voltage  $(V_T)$ , the voltage drops across the wire resistance  $(W_{R1}$  and  $W_{R2})$ , and receiver resistor  $(R_R)$ . In equation form:

EQ1

$$V_S = V_{WR1} + V_T + V_{WR2} + V_{RR}$$

# **NEXT ISSUE:**

Generating Precision Clocks for >1 GSPS Interleaved ADCs

# **Solutions for Pressure Force Load Testing**

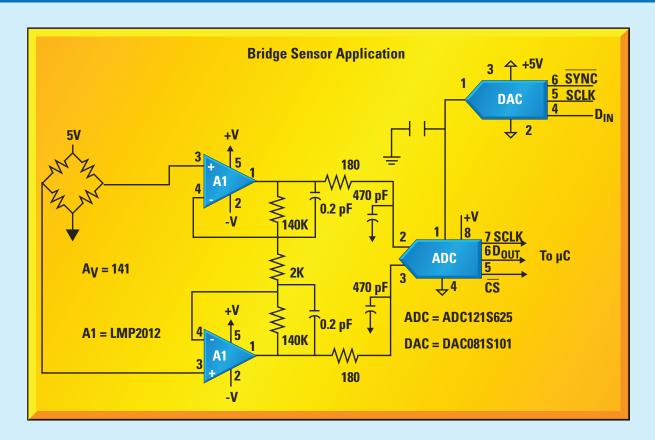

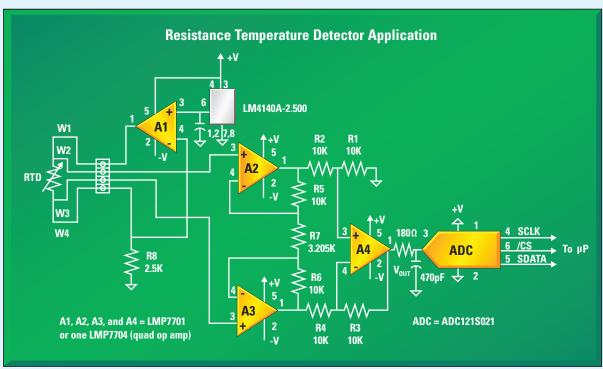

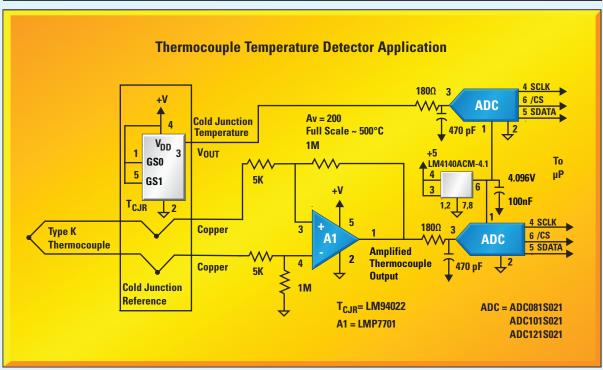

# **LMP2012 Precision Op Amp**

- · Auto zero dual op amp

- Input offset voltage,  $V_{OS},$  (36  $\mu V$  MAX) minimizes signal amplification errors of original input

- $\bullet\,$  TCVos of 15 nV/°C maintains a stable  $V_{OS}$  over time and temperature

- CMRR and PSRR greater than 120 dB ensures accuracy over various common mode voltages and across its entire operating voltage range

- Gain bandwidth product and slew rate are best in class at 3 MHz and 4 V/µs

- Also available:

- LMP2011 (single) in SOIC-8 and SOT23-5 packaging

- LMP2014 (quad) in TSSOP-14 packaging

# ADC121S625 12-Bit A/D Converter

- 12-bit analog-to-digital converter

- True differential inputs

- Guaranteed performance from 50 kSPS to 200 kSPS

- Reference voltage between 500 mV and 2.5V

- · Binary 2's compliant

- SPITM/QSPITM/MICROWIRETM/DSP compatible

# DAC081S101 8-Bit D/A Converter

- Low power, 8-bit digital-to-analog converter

- ±0.75 LSB INL

- 3 µsec settling time

- Rail-to-rail voltage output

- SPITM/QSPITM/MICROWIRETM/DSP compatible

For FREE samples, datasheets, and more information, visit

www.national.com/adc

amplifiers.national.com

# SIGNAL PATH | designer

# **Low-Voltage Current Loop Transmitter**

Substituting the loop current and loop resistances into EQ1:

EQ2

$$V_S = I_L W_{R1} + V_T + I_L W_{R2} + I_L R_R$$

Given the wire's resistance in X Ohms per foot, the maximum loop current of 20 mA, the value of  $R_R$  equal to  $10\Omega$ , and the equal lengths of wire, EQ2 can be rearranged to calculate the maximum loop distance in terms the loop parameters:

EQ3

$$ft = \frac{V_S - V_T - 0.2}{0.04 (X \Omega/ft)}$$

EQ3 illustrates three ways to increase the maximum loop length: (1) increase the loop power supply voltage, (2) increase the wire gage, which will reduce the wire's ohms per foot, or (3) reduce the minimum voltage required for the current loop transmitter operation, which is the focus of the following section.

The use of low voltage amplifiers, such as the LMV951, and low drop out voltage regulators, such as the LP2951, can reduce the minimum voltage required for the current loop transmitter. *Figure 2* shows the schematic of a loop-powered 4 to 20 mA transmitter, which will function with a minimum of 1.9V, and a 4 to 20 mA receiver.

In this example, a temperature sensor, such as the LM94022, provides a signal for the transmitter.

The components A1, Q1, and R1 through R5 form a voltage-to-current converter. The noninverting input of A1, pin 3, is the summing node for three signals, the loop current, offset current, and sensor signal voltage. The resistor R2 is the current shunt that measures the current flowing in the loop and is fed back through R3. The total loop current is the sum of the currents flowing in resistor R2 and R3,  $I_L=I_{R2}+I_{R3}$ . The amplifier, A1, forces the voltages at its inputs, pins 3 and 4, to be equal by forcing more or less current through R2. The result is that R2 and R3 have the same voltage across them. The ratio of the currents in R2 and R3 is the inverse of the resistor ratio:

EQ4

$$\left(\frac{I_{R2}}{I_{R3}} = \frac{R_3}{R_2}\right)$$

This highlights that the current in R3 is also part of the voltage-to-current conversion and is not an error current. An error source that will affect the loop current is the offset voltage of amplifier A1, which will add an error current to the loop current. At the minimum loop current of 4 mA, the voltage V2 is very close to 0.040V.

Figure 2. Loop-Powered Transmitter Schematic

# **Solutions for Factory Automation**

For FREE samples, datasheets, and more information, visit

www.national.com/adc

www.amplifiers.national.com

# **Precision Op Amps**

| Product ID    | Max VOS<br>Room Temp (μV) | TCV <sub>OS</sub><br>(μV/°C) | Specified Supply<br>Voltage Range (V) | PSRR<br>(dB) | CMRR<br>(dB) | Gain<br>(dB) | GBWP<br>(MHz) | Voltage Noise<br>(nV/√Hz) | I <sub>BIAS</sub><br>Room<br>Temp (pA) |

|---------------|---------------------------|------------------------------|---------------------------------------|--------------|--------------|--------------|---------------|---------------------------|----------------------------------------|

| LMP2011/12/14 | 25                        | 0.015                        | 2.7 to 5.25                           | 120          | 130          | 130          | 3             | 35                        | -3                                     |

| LMP7701/02/04 | 200                       | 1                            | 2.7 to 12                             | 100          | 130          | 130          | 2.5           | 9                         | 0.2                                    |

| LMP7711/12    | 150                       | -1                           | 1.8 to 5.5                            | 100          | 100          | 110          | 17            | 5.8                       | 0.1                                    |

| LMP7715/16    | 150                       | -1                           | 1.8 to 5.5                            | 100          | 100          | 110          | 17            | 5.8                       | 0.1                                    |

# **Precision Current Sense Amps**

| Product ID | Input Voltage Range | TCV <sub>OS</sub> (µV/°C) | Fixed Gain (V/V) | Supply Voltage (V) | CMRR (dB) | Packaging |

|------------|---------------------|---------------------------|------------------|--------------------|-----------|-----------|

| LMP8275    | -2 to 16            | 30                        | 20               | 4.75 to 5.5        | 80        | SOIC-8    |

| LMP8276    | -2 to 16            | 30                        | 20               | 4.75 to 5.5        | 80        | SOIC-8    |

| LMP8277    | -2 to 16            | 30                        | 14               | 4.75 to 5.5        | 80        | SOIC-8    |

# Low-Voltage Op Amps

| Product ID | Typ Is/<br>Channel (μA) | Total Specified<br>Supply Range (V) | Max V <sub>OS</sub><br>(mV) | Max I <sub>BIAS</sub> Over<br>Temperature | Typ<br>CMVR (V) | GBW<br>(MHz) | Packaging         |

|------------|-------------------------|-------------------------------------|-----------------------------|-------------------------------------------|-----------------|--------------|-------------------|

| LMV651     | 110                     | 2.7 to 5.5                          | 1                           | 80 nA (typ)                               | 0 to 4.0        | 12           | SC70-5, TSSOP-14  |

| LMV791     | 1150/0.14               | 1.8 to 5.5                          | 1.35                        | 100 pA                                    | -0.3 to 4.0     | 17           | TS0T23-6, MS0P-10 |

| LMV796     | 1150                    | 1.8 to 5.5                          | 1.35                        | 100 pA                                    | -0.3 to 4.0     | 17           | S0T23-5, MS0P-8   |

| LMV716     | 1600                    | 2.7 to 5.0                          | 5                           | 130 pA                                    | -0.3 to 2.2     | 5            | MSOP-8            |

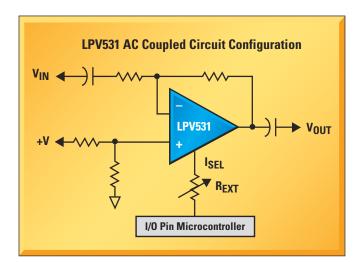

| LPV531     | 425                     | 2.7 to 5.5                          | 4.5                         | 10 pA                                     | -0.3 to 3.8     | 4.6          | TS0T23-6          |

# **ADCs for Single-Channel Applications**

|             |     |                |                            |                           |              |                         |             |                  | 1                 |                |

|-------------|-----|----------------|----------------------------|---------------------------|--------------|-------------------------|-------------|------------------|-------------------|----------------|

| Product ID  | Res | # of<br>Inputs | Pin/Function<br>Compatible | Throughput<br>Rate (kSPS) | Input Type   | Max Power<br>5V/3V (mW) | Supply (V)  | Max INL<br>(LBS) | Min SINAD<br>(dB) | Packaging      |

| ADC121S101  | 12  | 1              | <b>A</b>                   | 500 to 1000               | Single ended | 16/4.5                  | 2.7 to 5.25 | ±1.1             | 70                | S0T23-6, LLP-6 |

| ADC121S051  | 12  | 1              |                            | 200 to 500                | Single ended | 15.8/4.7                | 2.7 to 5.25 | ±1.0             | 70.3              | S0T23-6, LLP-6 |

| ADC121S021  | 12  | 1              |                            | 50 to 200                 | Single ended | 14.7/4.3                | 2.7 to 5.25 | ±1.0             | 70                | S0T23-6, LLP-6 |

| ADC101S101  | 10  | 1              |                            | 500 to 1000               | Single ended | 16/4.5                  | 2.7 to 5.25 | ±0.7             | 61                | S0T23-6        |

| ADC101S051  | 10  | 1              |                            | 200 to 500                | Single ended | 13.7/4.3                | 2.7 to 5.25 | ±0.7             | 60.8              | S0T23-6        |

| ADC101S021  | 10  | 1              |                            | 50 to 200                 | Single ended | 12.6/4                  | 2.7 to 5.25 | ±0.6             | 60.7              | S0T23-6        |

| ADC081S101  | 8   | 1              |                            | 500 to 1000               | Single ended | 16/4.5                  | 2.7 to 5.25 | ±0.3             | 49                | S0T23-6        |

| ADC081S051  | 8   | 1              |                            | 200 to 500                | Single ended | 12.6/3.6                | 2.7 to 5.25 | ±0.3             | 49                | S0T23-6        |

| ADC081S021  | 8   | 1              |                            | 50 to 200                 | Single ended | 11.6/3.24               | 2.7 to 5.25 | ±0.3             | 49                | S0T23-6        |

| ADC121S625* | 12  | 1              | <b>A</b>                   | 50 to 200                 | Differential | 2.8                     | 4.5 to 5.5  | ±1.0             | 68.5              | MSOP-8         |

| ADC121S705* | 12  | 1              | <b> </b>                   | 500 to 1000               | Differential | 16.5                    | 4.5 to 5.5  | ±.95             | 69.5              | MSOP-8         |

<sup>\*</sup>Differential input, 200 to 500 kSPS thruput rate forthcoming

# SIGNAL PATH | designer

# **Low-Voltage Current Loop Transmitter**

An offset voltage of 1 mV in A1 will cause an error of about 2.5% in I<sub>R3</sub>:

EQ5

$$\frac{0.001V}{0.040V} \times 100 = 2.5\%$$

Because the ratio of  $I_{R2}$  to  $I_{R3}$  is 1000 to 1, an error of 2.5% in  $I_{R3}$  results in a 0.0025% error in the loop current.

The voltage supply requirements for the components in transmitter must be evaluated in order to determine the minimum operating voltage required by the transmitter. For this example, a full-scale sensor input signal of 1.6V is used and results in a 10 mA per volt scale factor:

EQ6

$$\frac{I_L MAX - I_L MIN}{V_{IN} MAX - V_{IN} MIN} = \frac{20 \ mA - 4 \ mA}{1.6V - 0V} = \frac{16 \ mA}{1.6V} = 10 \ mA \ / V$$

The minimum voltage required for the transmitter (V3 – V1) is the highest voltage requirement of the two paths from V3 to V1. Path one is from V3 to Q1 and R2 to V1. At the maximum loop current of 20 mA, the voltage drop across R2 is 0.2V (V2) and a collector emitter voltage of about 0.5V to stay out of saturation is a total of 0.7V. The second path is V2 plus the output voltage of the voltage regulator and its dropout voltage. The full-scale sensor input signal of 1.6V requires about a 1.65V output from the regulator and the dropout voltage of the voltage regulator is less then 50 mV. The path has a minimum voltage requirement of 1.9V (0.2 + 1.65 + 0.05). Note that the minimum operating voltage of the LMV951 is 0.9V so the minimum transmitter voltage could be reduced to about 1.3V by increasing the scale factor to 18 mA per volt. This is supported by the voltage regulator, V<sub>R</sub>, which can be adjusted down to 1.25V, and with a drop out voltage of 50 mV, the loop transmitter can work down to 1.3V. The current loop transmitter functions by summing three signals: the loop current (R3), the offset current (R4), and the sensor (R5).

The loop current generates a voltage drop across resistor R2 such that V1 is negative with respect to V2 and then fed back through R3.

EQ7

$$V1=V2-R2(I_L)$$

The 4 to 20 mA current loop uses the offset current level of 4 mA to represent zero signal input. This is used as an open loop fault condition since zero current is a broken wire, transmitter failure, or another fault. The resistor R4 is connected to the output of the adjustable low drop-out voltage regulator to create the 4 mA offset current. Resistor R4, at 402 k $\Omega$ , sets approximately a 4 mA offset current when the output of the voltage regulator is 1.65V. The variable resistor R6 is used to set the loop current to 4 mA when the input signal is at zero volts. This adjustment compensates for error in the voltage regulator's output and resistor tolerance in R4, R5, and R7. The offset can be calibrated to 4 mA by measuring the voltage across R<sub>R</sub> and adjusting R6 until the voltage across R<sub>R</sub> is equal to 0.04V. The value of resistor R4 can be calculated for other supply voltages by equating the voltages at the amplifier's input pins and rearranging to solve for R4:

EQ8

$$R4 = \frac{R3 \times V_{OUT}}{R2 \times I_{R2}} - R_3$$

The resistor R5 is used to scale the signal input voltage to the 16 mA span of the loop current, and in this example, it is assumed the input signal span is 1.6V. The equation for calculating R5 can be developed by equating the voltages at the amplifier's input pins and rearranging to solve for R5.  $V_{\rm IN}$  is the maximum signal input, 1.6V for this example, and  $I_{\rm R2}$  is the change in output current, 16mA:

EQ9

$$R5 = \frac{R3 \times V_{IN}}{R2 \times I_{R2}}$$

This equation also indicates that changing the value of R5 can change the full-scale input voltage. A low resistance variable resistor could be used in

series with R5 to add a full-scale calibration as shown in the following schematic (*Figure 3*).

Figure 3. Input Calibration

In this example, a silicon temperature sensor is used as a signal source. The LM94022 is a low voltage, programmable gain temperature sensor that can be used to measure temperature from –50°C to 150°C. The schematic in *Figure 2* shows the LM94022's gain select pins connected to ground, or the lowest gain. With this gain, the sensor's output ranges from 1.299V for a temperature of –50°C to 0.183V for a temperature of 150°C.

As shown in *Figure 1*, the current loop transmitter accounts for only part of the voltage drop in the loop. The current loop receiver frequently uses a resistor, R<sub>R</sub> in *Figure 1*, to generate a voltage drop that is used to measure the loop current. The measurement of the voltage across R<sub>R</sub> can present some problems such as high common mode voltages, due to the loop power supply, as well as induced voltages from the environment. To overcome these measurement problems a differential amplifier, such as the LMP8270, can be used. The LMP8270 is a high common mode voltage differential amplifier with a fixed gain of 20. The gain of 20 also reduces the resistance of R<sub>R</sub>, which reduces the loop voltage drop.

Referring to *Figure 2*, the voltage across resistor R<sub>R</sub> is recovered from whatever common mode voltage exists on the current loop, up to 28V, and is amplified and drives the input to an Analog-to-Digital Converter (ADC). Internal to the LMP8270 is a differential amplifier with a gain of 10 followed by an amplifier with a gain of two. The internal connection between the two amplifiers is

brought out to pins 3 and 4. Also internal to the LMP8270 is a 100 k $\Omega$  resistor in series with the output of the first amplifier. A low pass filter is easily implemented by connecting a capacitor from pins 3 and 4 to ground.

Figure 2 shows a 4.096V reference being used by the ADC, representing the full-scale input. The differential input voltage to the LMP8270 for a 4.096V output is 4.096/20 = 0.2048V. The value of  $R_R$  for a voltage drop of 0.2048V at a current of 20 mA is 0.2048/20 = 10.24Ω. A 10Ω resistor is used because it is a standard precision value. The result is an output voltage from A2 of 0.8V to 4.0V for a loop current of 4 mA to 20 mA.

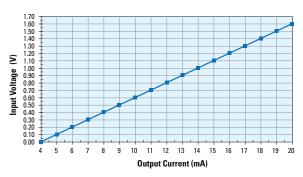

The current loop transmitter was calibrated using the end points, 0V and 1.6V, as the input voltages while measuring the voltage across the R<sub>R</sub> resistor. With 0.0V applied to the input the resistor R6 is adjusted until 40 mV is across R<sub>R</sub>. With 1.6V on the input, resistor R8, see *Figure 3*, is adjusted until 200 mV is across R<sub>R</sub>. *Figure 4* is the measured transfer function using a calibrated voltage source. The worst case deviation from a straight line was –8 µA, which is not observable on the graph in *Figure 4*.

Figure 4. Output Current vs Input Voltage

In summary, by using a selection of components that function with very low supply voltages a current loop transmitter can be designed that operates with as little as 1.3V.

View over 50 design seminars by industry experts. Log onto www.national.com/onlineseminars

# **Design Tools**

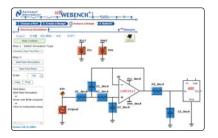

# **WEBENCH® Signal Path Designer® Tools**

Design, simulate, and optimize amplifier circuits in this FREE online design and prototyping environment allowing you to:

- Synthesize an anti-alias filter

- Select the best amplifier/ADC combo for your system specs

- Make trade-offs based on SNR, SFDR, supply voltage

- Simulate real-world operating conditions using SPICE

- Receive samples in 24 hours

webench.national.com

# **WaveVision 4.1 Evaluation Board**

Test and evaluate A/D converters with National's easy-to use WaveVision 4.1 evaluation board. Each evaluation board comes complete with USB cable and support software.

# **Features and benefits:**

- Plug-n-play ADC evaluation board

- USB 2.0 interface to PC

- PC-based data capture

- Easy data capture and evaluation

- Highlighted harmonic and SFDR frequencies

- Easy waveform examination

- Produces and displays FFT plots

- Dynamic performance parameter readout with FFT

- Produces and displays histograms

# **National Semiconductor**

2900 Semiconductor Drive Santa Clara, CA 95051 1 800 272 9959

### Mailing address:

PO Box 58090 Santa Clara, CA 95052

Visit our website at: signalpath.national.com

For more information, send email to:

new.feedback@nsc.com

# Don't miss a single issue!

Subscribe now to receive email alerts when new issues of Signal Path Designer® are available:

signalpath.national.com/designer

Also, be sure to check out our Power Designer! View online today at: power.national.com/designer

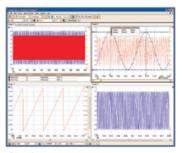

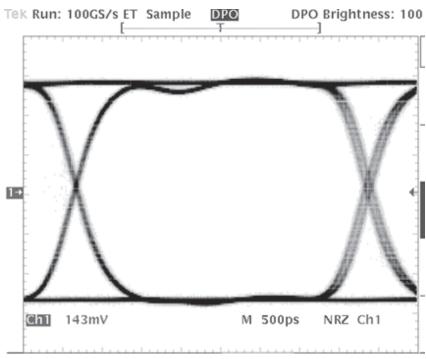

# Software tests compliance with eight popular protocols

This screen, obtained in a test of SATA-transmitted-signal out-ofband response, is typical of graphical results available from the QualiPHY compliance-test package.

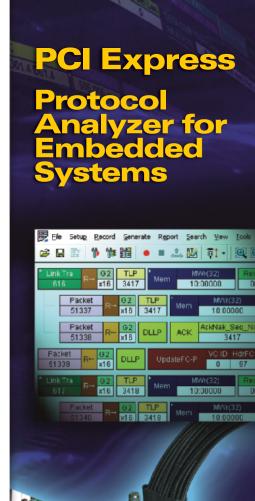

eCroy Corp's Windows-based QualiPHY, a hardware and software serial-data-compliance-test application, works with any of the company's 2-GHz or higher bandwidth real-time or sampling digital oscilloscopes and protocol analyzers. Targeting high-speed protocols, such as SATA (Serial Advanced Technology Attachment), FB-DIMM (fully buffered dual-inline-memory module), UWB (ultrawideband), Ethernet, USB, PCI Express, SAS (serial-attached small-computer-systems interface), and HDMI (high-definition-multimedia interface), the package provides digital- and analog-hardware engineers with an automated compliance-test tool for developing and validating devices' PHY (physical) layers in accordance with documents that the applicable standards organizations and special-interest groups have published.

QualiPHY features an intuitive graphical user interface that supports the industry's most popular serial-data standards and is common among them, eliminating the need for developers to learn new software for each project. Moreover, the expandable, modular architecture allows easy addition of support for more standards and suits the package to testing in such industry segments as

computers and computer equipment, wireless and mobile multiservice (voice/data) products and systems, cable and IPTV (Internet Protocol-television) set-top boxes, and vending and gaming machines. The package's developers also had today's globaldesign environment in mind. A development team can conduct tests anywhere in the world through the supported scopes' IEEE 488 or LAN/WAN (local/wide-area-network) connections, which permit live access to signals from scopes in remote locations.

By incorporating an application framework that enables users to save every experimental result to an XML (Extensible Markup Language)-formatted record, the product goes beyond mere reporting and tabulating of test results. The software offers a choice of automatic HTML (Hypertext Markup Language), PDF (portable-document-format), or RTF (rich-text-format) report generation. The reports contain tabulated numerical values for each test. This approach benefits IC developers, who require comprehensive wafer and die characterization to define parametric performance and establish device-performance capability; systemlevel-validation teams that work in parallel development cycles and must combine, study, and interpret performance data and correlate test results with earlier runs; and manufacturing and production tests, which use control charts and other performance indicators to monitor key parameters.

QualiPHY prices range from \$2995 each for versions that support USB and Ethernet to \$6995 for a version that supports UWB. All versions accommodate modules that add support for more -by Dan Strassberg standards.

**▶LeCroy Corp**, www.lecroy.com.

# - FEEDBACK LOOP

"I was thinking the other day about how long it will be before we embed **Bluetooth cell-phone transceivers** in our ears. Not much different from some of the ear piercings I see these days. I was thinking about how difficult it would be to replace batteries, but now I think scratching your ear once in a while may do the trick!"

—Chris Woolpert, in EDN's Feedback Loop at www.edn.com/ article/CA6399099. Add your comments.

# Low-cost, high-I/O-count FPGAs target display market

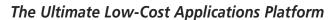

n an attempt to nab sockets in the market for lowcost, high-volume video displays, Xilinx has released an I/O-heavy version of its 90nm Spartan-3 FPGAs. Before this release, Xilinx introduced a high-gate- and high-pin-count version of the device, the Spartan-3. The company then followed it up with a logic-heavy version, Spartan-3E. Now, the company is introducing its high-I/O-count Spartan-3A devices, targeting I/O-intensive applications, most notably, the emerging video-display market in mainland China.

Mark Moran, senior strategic-marketing manager for the general-products division at Xilinx, says that the new 3A devices excel as bridging functions, in differential signaling, and as memory interfaces. Moran notes that, in many of today's applications, companies create one giant ASIC device for several product derivatives and then add functions and support to FPGAs in combination with the ASICs for new or emerging interfaces. Doing so allows users to keep the same footprint on a pc board but create derivatives or initiate field upgrades as needed.

To serve the bridging function, the 3A supports the most popular I/O standards, including PCI (Peripheral Component Interconnect), PCIe (PCI Express), USB, CAN (controller-area network), SPI, and I2C. To aid in differential signaling in displays, Xilinx has ensured that the device complies with both TMDS (transition-minimized differential signaling) and PPDS (point-to-point differential signaling). To help the larger chips adapt to the evergrowing and -changing memory world, Xilinx has added interfaces for DDR and DDR2.

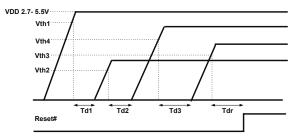

Spartan-3A devices include two hibernate modes; one for 40% static-power reduction and one for 99% static-power reduction. Both modes have a wake-up time of less than 100 msec. The Spartan-3A also includes "device DNA" to help companies protect the designs they implement on FPGAs from piracy or cloning. "Device DNA is a unique serial number within each FPGA," says Moran. "We program it in at manufacturing time. Then, we allow the users to determine what authentication mechanism they want to use." Users can choose from several types of encryption mechanisms. They can change the authentication encryption at any time and even in the field. "You can change it from design model to design model, so, if you are concerned about cloning, you can change it however and whenever you want to," Moran says. "Because it is incorporated in the design, you can fix it, so when the design does not authenticate, you can stop the system from functioning by telling the system to turn off one or several global controls in the FPGA. If there is one thing FP-GAs are not short on, it is global control."

You can also configure the authentication circuitry. "You can, for example, allow a contract manufacturer to access the full chip for test purposes for, say, eight minutes-enough time to test the chip in the context of the system but not enough time to copy the design," says Moran. "Now, you have the ability to stop cloning, reverse-engineering, and overbuilding."

Xilinx expects full production of the 700,000-system-gate XC3S700A and the 1.4 million-system-gate XC3S1400A to begin in the first quarter of this year. The company plans to have the rest of its Spartan-3As in production by the second quarter of this year. The company also plans to offer 50,000-, 200,000-, and 400,000-gate versions. Prices for the XC-3S700A and XC3S1400A devices are \$11.95 and \$16.95 (250,000), respectively. Starter kits are available now for \$199.

-by Michael Santarini >Xilinx, www.xilinx.com.

# DATA-ACQUISITION **MODULE FEATURES USB INTERFACE**

Targeting test, security, and industrial-control applications, Sealevel Systems recently announced the first in a family of USB-compatible data-acquisition and -control modules. The SeaDAC MIO-26 includes 16 single-ended or eight differential, 12-bit analog inputs; two 12-bit DAC outputs; eight optically isolated digital inputs; and eight open-collector digital outputs. You can independently software-select each ADC input-voltage range and configure the device for measuring a 0to 20-mA current loop.

The ADC channels feature 5-MHz bandwidth track/hold and 100ksample/sec throughput. The module's DAC channels are independently jumper-selectable for a 0 to 5 or a 0 to 10V output range. The digital inputs are 5 to 30V dc, and the open-collector outputs are suitable for switching the 24V devices you commonly find in industrial-control applications.

The SeaDAC MIO-26's standard operating-temperature range is 0 to 70°C, and an extendedtemperature range of -40to +85 $^{\circ}$ C is optional. Application software can use the vendor's SeaMax library or industry-standard Modbus protocol. The module comes with diagnostic utilities and sample programs. Prices for the SeaDAC MIO-26 start at \$479 (small volumes), and it is now available.

-by Warren Webb Sealevel Systems Inc, www.sealevel.com.

# **DILBERT By Scott Adams**

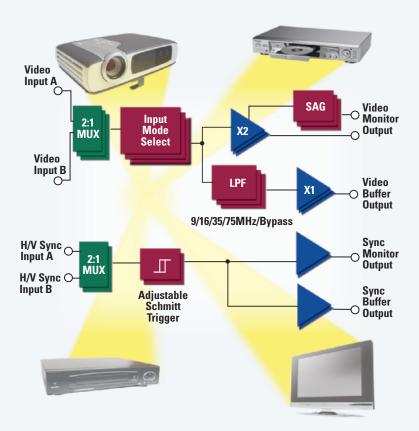

# First Triple Video Amp

# Integrates HV Sync, Filters and I<sup>2</sup>C Control

The **THS7327** from Texas Instruments integrates three analog video channels and two digital channels for HV sync, greatly simplifying system design and reducing component count. The three analog channels incorporate unity gain buffering and monitor feed-through paths to handle all standard video formats, including RGB, YPbPr and CVBS. Designers gain flexibility with the amplifier's I<sup>2</sup>C-programmable functions including: integrated 2:1 input multiplexers which enable switching of multiple video sources; fifth-order antialiasing filters to enable use with multiple video standards; and input bias modes.

# Applications

- Projectors

- Digital TVs

- Professional video systems

- Set-top boxes

- DLP® projectors/televisions

# **▶**Features

- 3 video amplifiers for CVBS, S-video, EDTV, HDTV and RGB

- HV sync paths with adjustable Schmitt Trigger

- 2:1 input MUX

- I<sup>2</sup>C control of all functions/all channels

- Integrated low-pass filters on ADC buffer path

- Selectable input bias modes

- Monitor pass-through function

- Passes input signal without filtering

- 500MHz bandwidth and 1300V/µs slew rate

- 6dB gain with SAG correction

- Pricing: \$3.35 in 1k units

For Samples, Evaluation

Modules and Technical

Information

www.ti.com/THS7327

800.477.8924, ext. 13477

# IEEE 802.11n wireless-LAN market remains in conflict as draft-n battle looms

oes the IEEE 802.11n wireless-LAN spec even matter? Yes, we could use faster wireless-LAN technology and better range. The speed mainly matters for video delivery, although a higher maximum bandwidth also means that an access point can support more users. In reality, however, the Wi-Fi community has settled into a comfort zone in which 802.11a will be the de facto technology standard for a long time. Backward compatibility with that standard may be more important than "draft compatibility" with the next standard. Nonetheless, chip vendors, including relatively unknown Ralink (www.ralinktech.com), have been relentlessly pushing new draft-n chips, and new end products will almost surely have arrived at the CES

(Consumer Electronics Show, www.cesweb.org), which took place in mid-January in Las Vegas.

Ralink claims that its new RT2800 chip set will offer the industry's longest range yet. To date, the company has had success primarily in valuepriced products as opposed to at the premium end of the price range in which vendors push range and speed advantages. The company can't explicitly describe the design elements that enable the range, so we'll again wait for end products to see how they fare. The company does appear to have a size advantage in that its chip set, with all the necessary antennas for both frequency bands that 802.11n products require, can fit into a typical USB-style Wi-Fi package.

In other recent activity,

Metalink (www.metalinkbb. com) revealed the second generation of its WLANPlus family, which also claims draft-n compatibility. Metalink targets consumer-electronics applications with claims that the product can carry HDTV streams. Marvell (www.marvell.com), meanwhile, announced that Gateway (www.gateway.com) would begin shipping PCs based on the draft-n Marvell TopDog chip.

But does draft-n status carry any credibility? With the 802.11n standard development stretching years beyond what it should have, the Wi-Fi Alliance (www.wi-fi.org) has announced plans for draft-n compliance testing, but that testing won't start until the second quarter of 2007, when, with any luck, the 2.0 draft of the 802.11n standard will achieve more

success at the ballot box. And one company, Airgo Networks (www.airgonetworks.com), has just announced its fourth-generation MIMO (multiple-input multiple-output) chip with the claim of draft 2.0 compatibility, despite the work that the standards body still needs to do.

The bigger news from Airgo, however, is that Qualcomm (www.gualcomm.com) recently acquired the MIMO pioneer. As noted on a recent EDN blog post, Qualcomm has in the past aggressively protected and profited from its IP (intellectual-property) portfolio, including CDMA (codedivision-multiple-access) technology for mobile phones. Airgo's MIMO IP could receive the same attention (www.edn. com/blog/150000015/post/ 1860005786.html). At least one other Wi-FI pundit, Wi-Fi Net News (http://wifinetnews. com/archives/007182.html), had the same thought.

-by Maury Wright

# PRACTICAL BOOK HELPS DEVELOPERS APPLY USB-INTERFACED MASS-STORAGE DEVICES

In technical writing, clarity is the name of the game. As someone who writes technical prose, I greatly admire Jan Axelson; she knows better than almost anybody else how to write clearly and how to explain complex technical issues so that her audience can understand them with minimal frustration. She has written many books on embedded-system topics, including USB Complete Third Edition (ISBN13 978-1-931448-02-4). Like her earlier books, her latest, USB Mass Storage: Designing and Programming Devices and Embedded Hosts (ISBN: 1-931448-04-3),

USB Mass practical guide to applying that interface using the ubiquitous bus.

aims at a person with a full plate of development work and looming deadlines who needs examples of practical ways to solve real and common problems.

The \$29.95, 287-pg paperback is a guide to designing and programming devices that implement storage functions, including devices that transfer data through the USB interface. Storage devices include drives of all types, as well as many cameras, data loggers, and other devices that perform dedicated functions. Using flash memory and other current technologies, even the smallest devices can store lots of data. The

book shows how to choose storage media, how to interface the media to a microcontroller or another CPU, and how to write device firmware to access the media and use USB to transfer data to and from storage. A comparison of media types helps in selecting media for a project. The media that Axelson considers include hard drives and flash-memory cards, such as the MMC (MultiMediaCard), SD (Secure Digital) Card, and CF (CompactFlash) cards. You will also learn what's involved in developing an embedded host that accesses off-the-shelf USB drives

Covered protocols include the bulk-only transport protocol for the USB mass-storage class, SCSI (smallcomputer-system-interface) commands that USB mass-storage devices support, the MMC commands and SPI (serial-peripheral-interface) protocol that MMCs and SD Cards support, and FAT (file-allocationtable) systems for accessing files and directories. Code examples show how to implement the protocols. To complement the book, Axelson maintains a Web page (www.lvr.com/mass\_storage.htm) with links to articles, program code, and other areas of interest to USB mass-storage developers. -by Dan Strassberg

Lakeview Research LLC, www.lvr.com.

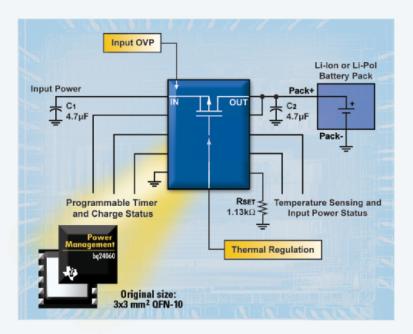

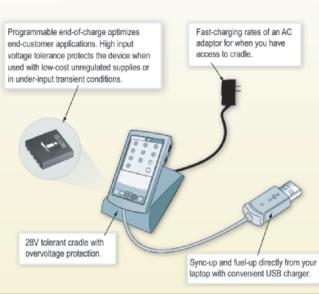

# Safer, Faster, Cooler Charging

# 1-A Single-Chip Li-Ion Charger with Thermal Regulation

The new **bq24060** highly integrated Li-Ion and Li-Pol linear charger IC from Texas Instruments is ideal for space-limited portable applications. It offers a variety of thermal regulation and safety features, including over-voltage protection. Additionally, the bq24060 can be configured in LDO mode to power the system when the battery is absent.

# **TI Battery Charging IC Solutions:**

| <b>Linear Charg</b> | ers            |                      |                       |                                                      |                     |

|---------------------|----------------|----------------------|-----------------------|------------------------------------------------------|---------------------|

| Device              | Li-lon         | Input<br>Voltage (V) |                       |                                                      | Package             |

| bq24080             | 1-Cell         | 4.5 - 6.5            | 1                     | Min. Current and Timer                               | 3 x 3<br>QFN-10     |

| bq24060             | 1-Cell         | 3.5 - 16.5           | 1                     | Min. Current<br>and Adj. Timer                       | 3 x 3<br>QFN-10     |

| bq24030             | 1-Cell         | 4.35 - 16            | 1.5                   | Min. Current<br>and Adj. Timer                       | 3.5 x 4.5<br>QFN-20 |

| Switch-Mod          | e Chargers     |                      |                       |                                                      |                     |

| Device              | Li-lon         | Input<br>Voltage (V) | Charge<br>Current (A) | Charge<br>Termination                                | Package             |

| bq24105             | 1-, 2-, 3-Cell | 4.35 - 16            | 2                     | Min. Current<br>and Adj. Timer<br>or Host Controlled | 3.5 x 4.5<br>QFN-20 |

| bq24721             | 3-, 4-Cell     | 0 - 24               | 7                     | Host Controlled through SMBus                        | 5 x 5<br>QFN-32     |

# ▶ Applications

- Smartphones, PDAs

- Bluetooth headsets

- MP3 players

- Digital cameras

- Handheld devices

### ▶ Features

- Over-voltage protection

- Thermal regulation

- LDO mode operation

- Integrated charge FET, reverse leakage protection and current sensor

- Price: \$1.20 in 1k units

Power Management Selection Guide

Datasheets, Samples and Evaluation Modules

www.ti.com/battman o 800.477.8924, ext. 3491

# Model-based DFM platform emerges

■DA start-up Clear Shape Technologies, the worst-kept secret in the DFM (design-for-manufacturing) market, in November formally announced itself and its two DFM tools. In 2003, industry veterans Atul Sharan, Yao-Ting Wang, and Fang-Cheng Chang, respectively chief executive officer, chief technology officer, and vice president of engineering, founded the company with the idea that advanced process technologies at 65-nm and smaller processes will require model-based physical verification, not just rule-based DRC (design-rule checking). "We've been around for three years now and haven't announced ourselves until now because DFM requires complex engagements," Sharan says. "You have to get validated in the fabs and create a tool that is production-ready."

Indeed, the three largest fabless companies offering 65-nm technologies-TSMC (Taiwan Semiconductor Manufacturing Co, www.tsmc.com); UMC (United Microelectronics Corp, www.umc.com); and the common process alliance of Chartered Semiconductor (www.charteredsemi.com), IBM (www.ibm.com), and Samsung (www.samsung.com) have endorsed Clear Shape's tools. Qualcomm (www.qualcomm.com), NEC (www.necel. com), and an unnamed company are currently using the tools. The unnamed entity is likely ATI (www.ati.amd.com), which Clear Shape quotes in its press materials.

Sharan says that, although most vendors offering DFM tools claim that IC designers are using their tools, most tools find use with maskdata-prep engineers, mask makers, or the foundries themselves. Sharan notes that many of the "DFM companies" that Synopsys (www. synopsys.com), Cadence (www.cadence.com), and Mentor (www.mentor.com) acquired last year fix OPC (optical-proximity-correction) and PSM (phase-shift-mask) tools in the mask-making process. Clear Shape's tools, according to Sharan, are true DFM tools, because they bring process models of lithography, RET (resolution-enhancement technology), OPC, CMP (chemical-mechanical polishing), mask, etch, interconnect parasitics, and transistor modeling to physical design and verification to help IC designers ensure that the fab they are targeting can manufacture their designs.

Clear Shape based its tools on a patent-pending, modelbased, nonlinear opticaltransformation algorithm. "We give the designer the ability to go from ideal GDSII [Graphic Design System II] to actual predictive-silicon-based design," Sharan says. "We've created a platform to essentially manage all aspects of variability as they effect design. The primary causes of variability arise from the technology or process issues from the process side." He says that designers must comprehend those issues and then account for those for variability on every axis: timing, leakage power, signal integrity, and catastrophic failures.

The Clear Shape platform currently includes the OutPerform and InShape tools. Cell, IP (intellectual-property), custom-analog, and cell-based digital designers can use OutPerform during physical design. Cell-based-chip designers input their DEF (Data Exchange Format), SPEF (Standard Parasitic Exchange Format), library information, and fab-DFM technology files into OutPerform. The tool then identifies timing- and leakageparametric hot spots for violations due to systematic variations. The tool also calculates the change in delay and timing skew based on the in-context shape variations and provides delay variations back to static-timing-analysis tools in the form of an incremental SDF (Standard Delay Format).

For custom and analog flows, users feed the tool a Spice netlist and Spice models. The tool then predicts current density across channels, extracting transistor parameters for transistors from the embedded InShape-model-based siliconcontour-prediction engine. The tool then produces a back-annotated-transistor-Spice netlist and applies the changes in RC data to the designer's existing DSPF (Detailed Standard Parasitic Format) or SPEF file to represent the true effects of in-context silicon-shape variations without creating new nodes or parasitic elements. Designers can then simulate the back-annotated-transistor-Spice netlist with their Spice simulators to check the effect of variations on their designs and detect potential failures before going to silicon.

InShape is, in effect, a fullchip DRC/LVS (layout-versus-schematic) checker, which catches the problems that rules-based tools can't, according to Clear Shape. Whereas

DRC and LVS tools confirm that a design conforms to an ever-growing set of foundry rules for a given process, In-Shape checks each layer of a design to ensure that elements conform to actual fab-process models.

Rules-based engines apply an ever-growing list of rules across an entire design and do not account for in-context or situational issues that may impact every design, says the company's vice president of marketing, Nitin Deo. "In the absence of knowing what the design is going to look like, you can have a design that is DRC-clean, but what you get is silicon that encounters catastrophic failures and parametric failures," Sharan says.

During physical verification, designers use InShape to scan their entire design-both device and interconnect-to identify structures that will later cause problems in RET, OPC, mask, etch, and lithography. The tool then automatically generates a set of "fixing guidelines" that designers can use to implement changes in third-party place-and-route tools. The tool can also produce a critical dimension report that designers can feed into OutPerform.

Sharan stresses that the tool doesn't create rigid guidelines; rather, it produces a DFM-hotspot list and ranks issuesopens and shorts, contact coverage, gate variability, and lineend pullback in the designers' original layout-by type and criticality. Designers can also use the tool's contour-prediction features to do what-if analysis. Prices for OutPerform and In-Shape start at \$300,000 each per master license per year.

-by Michael Santarini Clear Shape Technologies, www.clearshape.com.

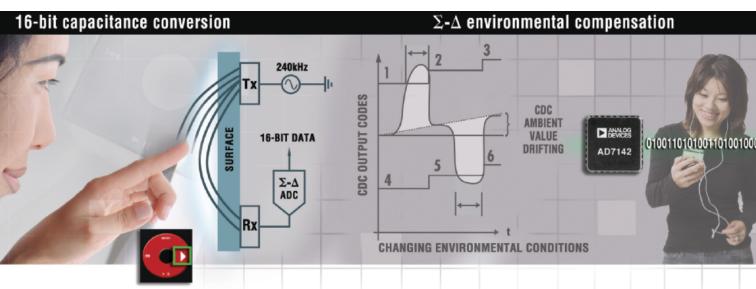

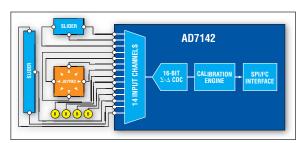

# 16-bit touch controller for the best user experience. In data conversion, analog is everywhere.

# 16-bit $\Sigma$ - $\Delta$ CDC ...

- <1 femtofarad resolution</li>

- Full power mode: <1 mA

- Low power mode: 50 μA

- Shutdown current: <2 μA

- Supply voltage: 2.6 V to 3.6 V

- Automatic environmental calibration

- · Automatic adaptive sensitivity

- SPI® or I2C® interface

- $\bullet$  32-lead 5 mm imes 5 mm LFCSP

- Price: \$1.65 (1k quantities)

# ... enabling multiple applications

- Consumer electronics

- · Medical instrumentation

- · Automotive applications

- · Industrial equipment

- PC peripherals

With 14 inputs, the AD7142 can be programmed for a variety of navigation functions including buttons, sliders, scroll wheels, and joypads.

# Improved sensitivity and environmental calibration—made possible by $\Sigma$ - $\Delta$ conversion

For products with increasing feature convergence, finger-driven navigation enhances the user experience—for designers as well as consumers. The AD7142 capacitance-to-digital converter (CDC) with on-chip environmental compensation delivers unmatched touch control performance. It offers:

- · Reliable performance over supply and temperature

- · Programmable functionality and touch sensitivity

- 50% lower power than competitive solutions

- Development tools, such as reference designs and host software, that reduce time to market

ADI also offers CDC solutions for measuring proximity, position, level, pressure, and humidity.

#### New online seminar:

View the "Innovative Human Interface Design Techniques Using CDCs" seminar at www.analog.com/onlineseminar-CDC.

# **VOICES**

# Cherokee International: Where in the world are design and manufacturing?

hen electronic-hardware companies perform research on where to build manufacturing facilities, they must consider more than just which country has the cheapest labor rates. In this brave new world of electronics design and manufacturing, concerns such as a country's technology, supply-chain infrastructure, point of consumption, and flexibility are equally important.

Cherokee International (www.cherokeepwr.com), a vendor of ac/dc- and dc/dc-power supplies, is no neophyte to offshore manufacturing: With its headquarters in Tustin, CA, Cherokee has design centers and manufacturing throughout the world. Tustin, CA, and Wavre, Belgium, are design centers and manufacturing locations for high-volume, low-mix quantities. Cherokee's Guadalajara, Mexico, facility has in the past handled the company's higher volume products, and its facility in Bombay, India, has long manufactured its magnetic components. Recently, Cherokee underwent a re-evaluation of its operations, so it performed a global analysis of where to locate its next generation of manufacturing and design. At first glance, Mexico seemed the logical place to expand design and manufacturing. However, considering proximity to the customer, the opportunity to call on the Asian market, and other factors, Cherokee decided to build in Shanghai, China. EDN asked Mike Wagner, vice president of marketing and an electrical engineer who started out as a power-supply designer, what led to Cherokee's change of manufacturing strategy.